[사회] 한양대 유호천 교수팀, 가우시안-시그모이드 강화 트랜지스터 개발

-

3회 연결

본문

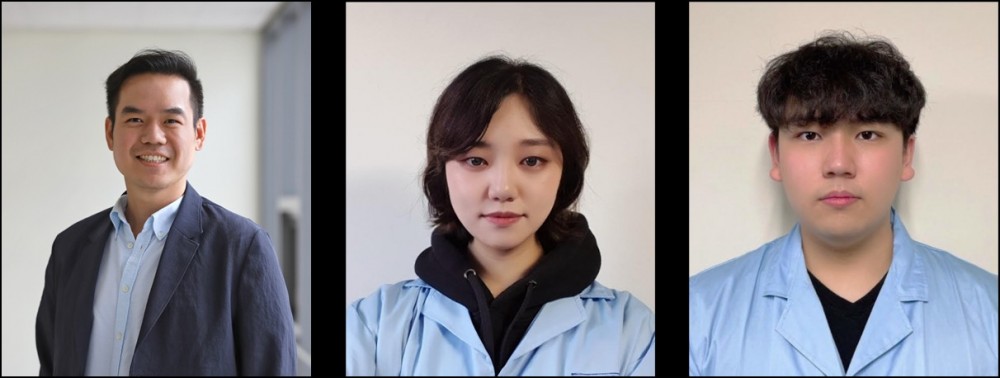

(좌측부터) 유호천 교수, 박지수 석사과정생, 서주형 박사과정생

한양대학교 융합전자공학과 유호천 교수 연구팀이 성균관대학교 신원준 교수, 미국 일리노이 시카고대 Amit R. Trivedi 교수 연구팀과 공동으로 게이트 전압 조절만으로 Gaussian(정규분포)과 Sigmoid(S자형) 두 가지 활성화 함수를 하나의 소자에서 구현하는 '가우시안-시그모이드 강화 트랜지스터(Gaussian-Sigmoid Reinforcement Transistor, GS-RT)'를 개발했다고 17일 밝혔다.

이 소자는 단일 트랜지스터 내에서 필요한 활성화 함수를 자유롭게 전환할 수 있는 구조로, 인공지능 강화학습 알고리즘에서 핵심적인 ‘탐색-활용’ 균형 문제를 하드웨어적으로 해결할 수 있는 것이 특징이다. 연구팀은 이번 기술을 통해 강화학습 기반 AI 시스템의 회로를 크게 단순화하면서도 학습 효율과 성능을 향상시킬 수 있을 것으로 기대하고 있다.

기존 강화학습 시스템에서는 가우시안과 시그모이드 함수가 주로 사용되나, 이를 하드웨어로 구현하기 위해서는 복잡한 연산과 수십 개의 트랜지스터가 필요해 전력 소모와 설계 난이도가 큰 한계로 작용해 왔다. 특히 두 함수가 모두 요구되는 회로 구성은 칩 면적과 자원 부담이 커 효율적인 AI 반도체 설계에 제약이 컸다.

이에 연구팀은 산화물 반도체(IGZO)와 유기 반도체(DNTT)를 수직 적층한 n–p–i–p 이종접합 구조에 절연층과 비대칭 전극을 적용, 게이트 전압만으로 소자가 시그모이드 또는 가우시안 전류 특성을 나타내도록 설계했다. 이를 통해 기존 복잡한 회로를 단일 소자만으로 대체할 수 있는 뉴로모픽 연산에 최적화된 구조를 구현했다.

GS-RT 소자는 강화학습 실험을 통해 실효성이 입증됐다. 멀티암드 밴딧 문제에서 기존 방식 대비 약 20% 빠른 학습과 30% 높은 보상을 달성했으며, 카트폴 실험에서도 표준 ReLU 대비 빠른 수렴 속도와 잡음 환경에서도 높은 안정성을 보였다. 이는 GS-RT의 비선형 곡선 특성이 학습 과정에서 안정적인 그래디언트 흐름을 제공하기 때문으로 분석된다.

연구 책임자인 유호천 교수는 “이번 연구는 게이트 전압만으로 한 개의 소자에서 두 가지 활성화 함수를 구현해 낸 AI 반도체 기술의 새로운 가능성을 제시한 사례”라며, “향후 강화학습을 포함한 인공지능 신경망 연산, 뉴로모픽 시스템, 초저전력 엣지 컴퓨팅 등 차세대 AI 반도체 분야에서 하드웨어 기반의 효율적인 컴퓨팅 솔루션으로 활용될 것으로 기대한다”고 밝혔다.

이번 연구는 과학기술정보통신부·정보통신기획평가원(IITP)의 인공지능반도체 고급인재양성 사업 및 한국연구재단(NRF) 사업 등의 지원을 받아 수행됐으며, 연구 성과는 재료·전자소자 분야 국제학술지 『Advanced Functional Materials』(IF: 19.0, JCR 상위 5%) 2025년 7월호에 게재됐다.

해당 논문 “Gaussian-Sigmoid Reinforcement Transistors: Resolving Exploration-Exploitation Trade-Off Through Gate Voltage-Controlled Activation Functions”에는 유호천 교수 연구실 박지수 석사과정생이 제1저자, 서주형 박사과정생이 공동 제1저자로 참여했고, 유호천 교수가 교신저자로 참여했다.

댓글목록 0